DSPIC33EP128GP502-E/SS – Microchip

$61.80

- Descrição

- Investigação

Descrição

O dispositivo DSPIC33EP128GP502-E/SS é um microcontrolador de 16 bits (MCU) desenvolvido pela Microchip Semiconductor Corporation.

| Tamanho da memória RAM | 8K x 16 |

| Número de bits | 16 |

| Número de ADCs | 1 |

| Temperatura de operação (Máx.) | 125 ℃ |

| Temperatura de operação (Mín.) | -40 ℃ |

| Estilo de montagem | Montagem em superfície |

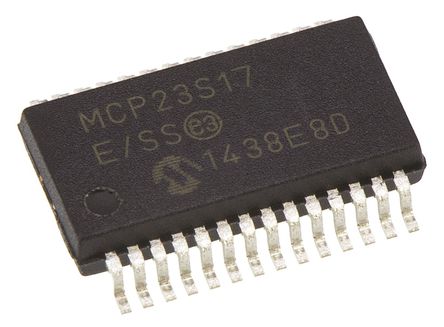

| Encapsulamento / pacote | SSOP-28 |

| Temperatura de operação | -40℃ ~ 125 ℃ |

| Status do ciclo de vida do produto | Ativo |

| Embalagem | Tubo |

| RoHS | Compatível com RoHS |

Condições de funcionamento

- 3.0V a 3,6 V, -40°C a +85°C, DC para 70 MIPS

- 3.0V a 3,6 V, -40°C a +125°C, DC para 60 MIPS

Essencial: 16-Pedaço CPU dsPIC33E/PIC24E

- Código Eficiente (C e montagem) Arquitetura

- Dois acumuladores de 40 bits

- Ciclo Único (MAC/MPY) com busca dupla de dados

- Ciclo Único, MUL de sinal misto mais divisão de hardware

- 32-Suporte para multiplicação de bits

Gerenciamento de relógio

- 1.0% Oscilador Interno

- PLLs programáveis e fontes de clock oscilador

- Monitor de relógio à prova de falhas (FSCM)

- Temporizador de vigilância independente (WDT)

- Despertar e iniciar rapidamente

Gerenciamento de energia

- Modos de gerenciamento de baixo consumo de energia (Dormir, Parado, Cochilar)

- Reinicialização de inicialização integrada e reinicialização de queda de energia

- 0.6 Corrente Dinâmica mA/MHz (típica)

- 30 μA IPDCcorrente (típica)

PWM de alta velocidade

- Até três pares PWM com temporização independente

- Tempo morto para subidas e descidas

- 7.14 ns Resolução PWM

- Suporte PWM para:

– CC/CC, CA/CC, Inversores, PFC, Iluminação

– BLDC, PMSM, OLHO, SRM

- Entradas de falha programáveis

- Configurações flexíveis de gatilho para conversões ADC

Recursos analógicos avançados

- Módulo ADC:

– Configurável como 10 bits, 1.1 Msps com quatro S&H ou

12-pedaço, 500 ksps com um S&H

– Seis entradas analógicas em dispositivos de 28 pinos e até

16 entradas analógicas em dispositivos de 64 pinos

- Fontes de disparo ADC flexíveis e independentes

- Até três amplificadores operacionais/comparadores com

Conexão direta ao módulo ADC:

– Comparador dedicado adicional

– Referências programáveis com 32 pontos de tensão

- Unidade de medição de tempo de carga (CTMU):

– Suporta detecção de toque capacitiva mTouch™

– Fornece medição de tempo de alta resolução (1 ns)

– Medição de temperatura no chip

Temporizadores/Comparação de Saída/Captura de Entrada

- 12 Temporizadores de uso geral:

– Cinco temporizadores/contadores de 16 bits e até dois de 32 bits

– Comparação de quatro saídas (OC) módulos, configurável

como temporizadores/contadores

– Módulo PTG com dois temporizadores/contadores configuráveis

– 32-Interface do codificador de quadratura de bits (QUEM) módulo,

configurável como temporizador/contador

- Captura de quatro entradas (CI) módulos

- Seleção de pino periférico (PPS) para permitir o remapeamento da função

- Gerador de gatilho periférico (PTG) para agendamento

Sequências Complexas

Interfaces de comunicação

- Dois módulos UART (17.5 Mbps):

– Com suporte para protocolos LIN/J2602 e IrDA

®

- Dois módulos SPI de 4 fios (15 Mbps)

- Módulo ECAN™ (1 Mbaud) Suporte CAN 2.0B

- Dois módulos I2C™ (até 1 Mbaud) com suporte SMBus

- PPS para permitir remapeamento de funções

- Verificação de redundância cíclica programável (CDC)

Acesso direto à memória (DMA)

- 4-Canal DMA com arbitragem prioritária selecionável pelo usuário

- UART, IPS, ADC, ECAN, CI, OC e temporizadores

Entrada/Saída

- Pia/Fonte 12 mA ou 6 mA, Pino específico para VOH/VOL padrão, até 22 ou 14 mA,respectivamente para VOH1 não padrão

- 5Pinos tolerantes V

- Seleção de pino periférico (PPS) para permitir a função digital

Remapeamento

- Dreno aberto selecionável, Pull-ups e pull-downs

- Até 5 Corrente do grampo de sobretensão mA

- Alterar interrupções de notificação em todos os pinos de E/S

Qualificação e Suporte Classe B

- AEC-Q100 REVG (Nota 1, -40°C a +125°C) Planejado

- AEC-Q100 REVG (Nota 0, -40°C a +150°C) Planejado

- Biblioteca de Segurança Classe B, CEI 60730

Suporte ao desenvolvimento do depurador

- Programação no circuito e na aplicação

- Dois programas e dois pontos de interrupção de dados complexos

- IEEE 1149.2 Compatível (JTAG) Varredura de limite

- Monitoramento de rastreamento e tempo de execução